操作系统 什么是交叉存储器

交叉存储器旨在弥补动态随机访问存储器(DRAM)或核心存储器的相对较慢速度,通过均匀分布内存地址在内存库之间。这样,连续的内存读取和写入使用每个内存库,由于等待内存库准备好进行操作的时间减少,从而实现更高的内存吞吐量。

与多通道存储器架构不同,交叉存储器主要是因为在主存储器和内存控制器之间并未添加更多通道。但是,通道交错也是可能的,例如,在 Freescale i.MX6处理器中,允许在两个通道之间进行交错。使用交叉存储器,内存地址被分配给每个内存库。

交错内存的示例

这是一种将内存分成多个模块的抽象技术,使地址空间中的连续单词放置在不同的模块中。

假设我们有4个内存银行,每个银行含有256个字节,那么在块定向方案(不交错)中,虚拟地址0到255将分配给第一个银行,虚拟地址256到511将分配给第二个银行。但是在交错内存中,虚拟地址0将与第一个内存银行一起,虚拟地址1将与第二个内存银行一起,虚拟地址2将与第三个内存银行一起,虚拟地址3将与第四个内存银行一起,然后虚拟地址4又与第一个内存银行一起。

因此,CPU可以立即访问交替的部分,而无需等待内存缓存。有多个内存银行交替提供数据。

在上述4个内存银行的示例中,虚拟地址0、1、2和3所在的数据可以同时访问,因为它们存在于不同的内存银行中。因此,我们不需要等待完成数据提取才能开始下一次操作。

具有n个银行的交错内存被称为 n路交错 。在交错内存系统中仍然有 两个DRAM银行 ,但从逻辑上看,系统似乎只有一个大小加倍的内存银行。

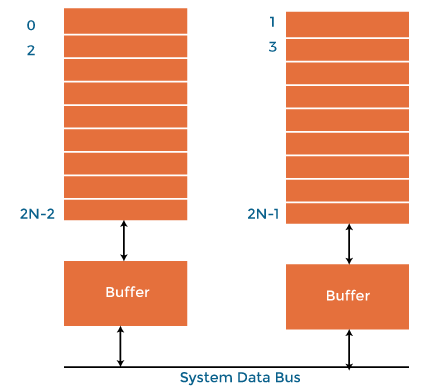

在下面的2个内存银行的交错银行表示中,银行0的第一个长字由银行1的第一个长字紧接着,然后是银行0的第二个长字,然后是银行1的第二个长字,依此类推。

下图显示了n个长字的两个物理银行的组织结构。逻辑银行的所有偶数长字位于物理银行0中,而所有奇数长字位于物理银行1中。

为什么我们要使用内存交错

当处理器从主存中请求数据时,一块数据会被传送到缓存,然后再传送给处理器。所以每当发生缓存未命中时,数据需要从主存中获取。但是主存的速度相对较慢,因此为了提高主存的访问速度,我们使用了内存交错。

例如,我们可以同时访问所有的四个模块,从而实现并行处理。可以使用高位来从模块中获取数据。这种方法可以有效地利用内存。

内存交错的类型

在操作系统中,有两种类型的内存交错:

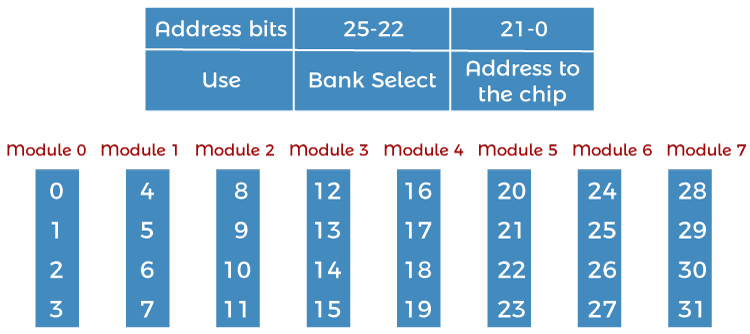

1. 高阶交错: 在高阶内存交错中,内存地址的最高位决定了一个特定位置所在的内存块。而在低阶内存交错中,内存地址的最低位决定了内存块。

最低位将被发送作为地址给每个芯片。一个问题是连续的地址往往会在同一个芯片上。数据传输的最大速率受到内存周期时间的限制。这也被称为 内存分块(Memory Banking) 。

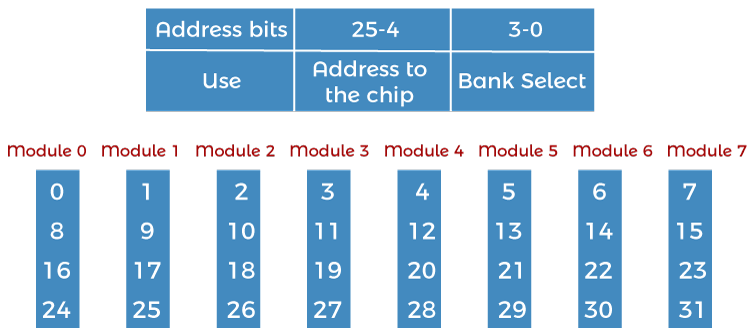

2. 低位序列交错: 最低有效位选择低位序列交错中的内存模块。在这种情况下,连续的内存地址位于不同的内存模块中,可以实现比循环时间更快的内存访问。

分页内存的好处

指令流水线可能需要同时从主存获取指令和操作数,这在传统的内存访问方法中是不可能的。同样,算术流水线需要同时从主存中获取两个操作数。因此,为了解决这个问题,内存交织技术应运而生。

- 它允许同时访问内存的不同模块。模块化存储技术允许CPU在一个模块忙于读取或写入操作时,与另一个模块进行内存访问。因此,我们可以说交织内存在其他模块的状态下满足每个内存请求。

- 因此,由于这个明显的原因,交织内存使系统比非交织内存更具响应性和速度。此外,随着同时访问内存,CPU处理时间也减少并增加吞吐量。交织内存在具有流水线和向量处理的系统中很有用。

- 在交织内存中,连续的内存地址分布在不同的内存模块中。例如,在一个字节可寻址的4路交织内存中,如果字节0在第一个模块中,那么字节1将在第二个模块中,字节2将在第三个模块中,字节3将在第四个模块中,再一次字节4将在第一个模块中,如此往复。

- 一个n路交织内存,其中主内存被划分为n个存储器和系统可以同时从n个不同的存储器中访问n个操作数/指令。这种存储器访问可以将内存访问时间减少一个接近存储器数量的因素。在这种内存交织中,内存位置i可以在存储器 i mod n 中找到。

交织DRAM

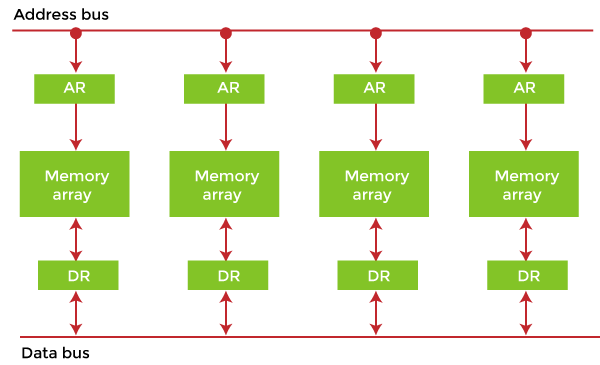

主内存通常由一组DRAM内存芯片组成,多个芯片可以组合在一起形成一个存储器。通过支持交织的存储器控制器,可以将这些存储器安排成交织的形式。

DRAM中的数据以页为单位存储。每个DRAM存储器有一个行缓冲区,用于访问存储器中的任何页。在读取DRAM存储器中的一页之前,它首先被加载到行缓冲区中。如果页面立即从行缓冲区中读取,则在一个内存周期内具有最短的内存访问延迟。假设这是一个行缓冲区不命中,也称为行缓冲区冲突。由于新页面必须在读取前加载到行缓冲区中,因此速度较慢。当在同一存储器库中服务于不同内存页面的访问请求时,会发生行缓冲区不命中。行缓冲区冲突会导致内存访问的延迟。相反,对不同存储器库的内存访问可以以高吞吐量并行进行。

在传统布局中,内存存储器可以分配一个连续的内存地址块,这对于存储器控制器来说非常简单,并且在完全随机访问场景中与通过交织实现的性能水平相当。然而,由于引用局部性,内存读取很少是随机的,并且在交织布局中优化接近的访问可获得更好的性能。

存储器的寻址方式不会影响已经缓存的内存位置的访问时间,只会影响需要从DRAM中检索的内存位置。

极客笔记

极客笔记