操作系统 TLB翻译查询缓冲器

分页的缺点

- 页面表的大小可能非常大,因此会浪费主存。

- 从主存读取单个字需要更长时间。

如何减小页面表的大小

- 通过增加页面大小可以减小页面表的大小,但这会导致内部碎片和页面浪费。

- 另一种方法是使用多级分页,但这会增加有效访问时间,因此不是一种实际的方法。

如何减小有效访问时间

- 处理器可以使用一个存储在其中的页面表寄存器,以便访问页面表的访问时间变得更短,但寄存器价格较高且相对于页面表的大小来说非常小,因此这也不是一种实际的方法。

- 为了克服分页中的这些缺点,我们必须寻找一种比寄存器更便宜且比主存更快的内存,以便降低处理器不断访问页面表的时间,并且只关注访问实际字。

引用的局部性

在操作系统中,引用的局部性的概念指出,操作系统可以只将CPU频繁访问的那些页面加载到主存中,并且还可以加载仅与那些页面对应的页表条目。

翻译查询缓冲器(TLB)

翻译查询缓冲器可以被定义为一种用于减少反复访问页面表所需时间的内存缓存。

它是一种靠近CPU的内存缓存,CPU访问TLB所需的时间少于访问主存所需的时间。

换句话说,我们可以说TLB比主存更快、更小,但比寄存器更便宜、更大。

TLB遵循引用的局部性原理,这意味着它只包含CPU频繁访问的那些页面的条目。

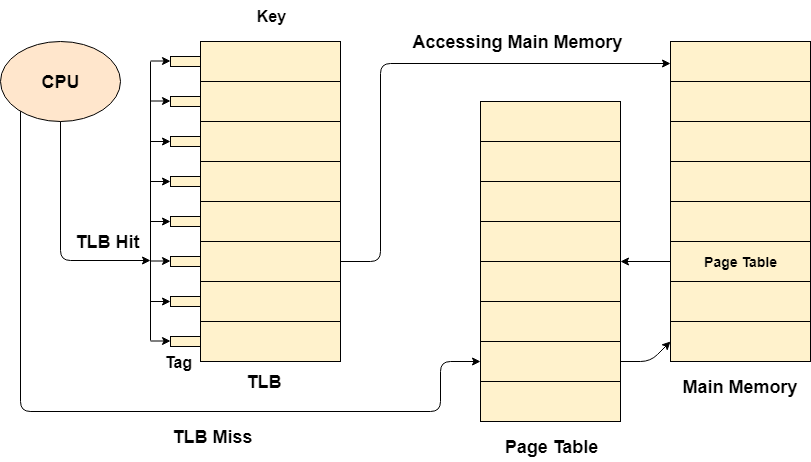

在翻译缓冲区中,有标签和键,通过它们进行映射。

TLB命中是指所需的条目在翻译缓冲区中找到。如果发生这种情况,则CPU只需访问主存中的实际位置。

但是,如果在TLB中找不到条目(TLB未命中),那么CPU必须访问主存中的页表,然后访问主存中的实际帧。

因此,在TLB命中的情况下,与TLB未命中的情况相比,有效访问时间将更少。

如果TLB命中的概率为P%(TLB命中率),则TLB未命中的概率(TLB未命中率)将为(1-P)%。

因此,可以将有效访问时间定义为;

EAT = P (t + m) + (1 - p) (t + k.m + m)

Where, p → TLB命中率, t → 访问TLB所需时间, m → 访问主内存所需时间 k = 1, 即实现了单层分页。

根据公式,我们可以得知:

- 如果TLB命中率提高,有效访问时间将会减少。

- 在多级分页的情况下,有效访问时间将会增加。

极客笔记

极客笔记